AMD近期获得一项关于“高带宽内存模组架构”的专利,旨在解决DDR5内存的性能瓶颈。新架构通过引入高带宽双列直插内存模组(HB-DIMM)结构,将内存传输速率从6.4 Gbps提升至12.8 Gbps,实现翻倍。该技术无需改变现有DRAM芯片设计,而是通过先进的数据缓冲芯片与多个DRAM器件集成耦合,优化信号完整性并降低延迟。其核心在于集成寄存器时钟驱动电路,通过解码内存指令和芯片标识位实现命令路由,支持将内存操作分配至多个独立寻址的“伪通道”,实现并行数据访问,突破传统顺序访问的带宽限制。该架构还具备1n/2n操作模式和简化的非交错传输格式,并在伪通道模式与四通道配置间动态切换,以适应高性能计算等对数据吞吐和灵活性要求高的场景。

🚀 **突破DDR5性能瓶颈**:AMD新专利技术旨在解决当前DDR5内存面临的性能瓶颈,通过创新的模组架构显著提升数据传输效率。

💡 **HB-DIMM架构与速率翻倍**:该技术引入了高带宽双列直插内存模组(HB-DIMM)结构,将内存总线的数据传输速率从现有的6.4 Gbps提升至12.8 Gbps,实现性能翻倍,且无需改变现有DRAM芯片设计。

🔗 **缓冲芯片与并行访问**:核心在于将多个DRAM器件与先进的数据缓冲芯片集成,缓冲芯片负责调度和管理信号传输,通过集成寄存器时钟驱动电路实现命令路由,支持将内存操作分配至多个独立寻址的“伪通道”,从而实现真正的并行数据访问,打破传统顺序访问的带宽限制。

⚙️ **灵活的模式与传输优化**:该架构支持1n与2n两种操作模式,具备更高的时钟同步和信号控制灵活性。同时,采用简化的非交错传输格式取代传统交错式配置,进一步减少了数据传输延迟。它还能在伪通道模式与四通道配置之间动态切换,以适应不同应用场景的需求,尤其适用于对数据吞吐和运行灵活性要求极高的环境。

2025-09-27 15:20:32 作者:狼叫兽

9月27日,有技术资料显示,AMD近期获得一项名为“高带宽内存模组架构”的专利授权,该技术旨在应对当前DDR5内存所面临的性能瓶颈问题。新架构可在不改变现有DRAM芯片设计的基础上,显著提升内存传输效率。

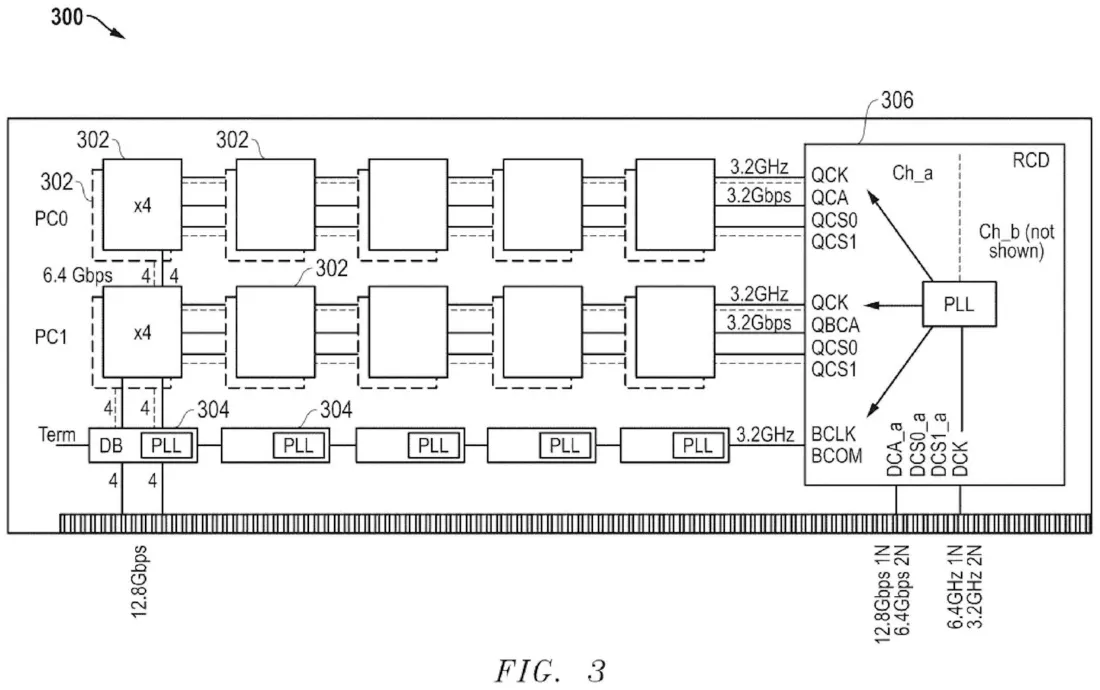

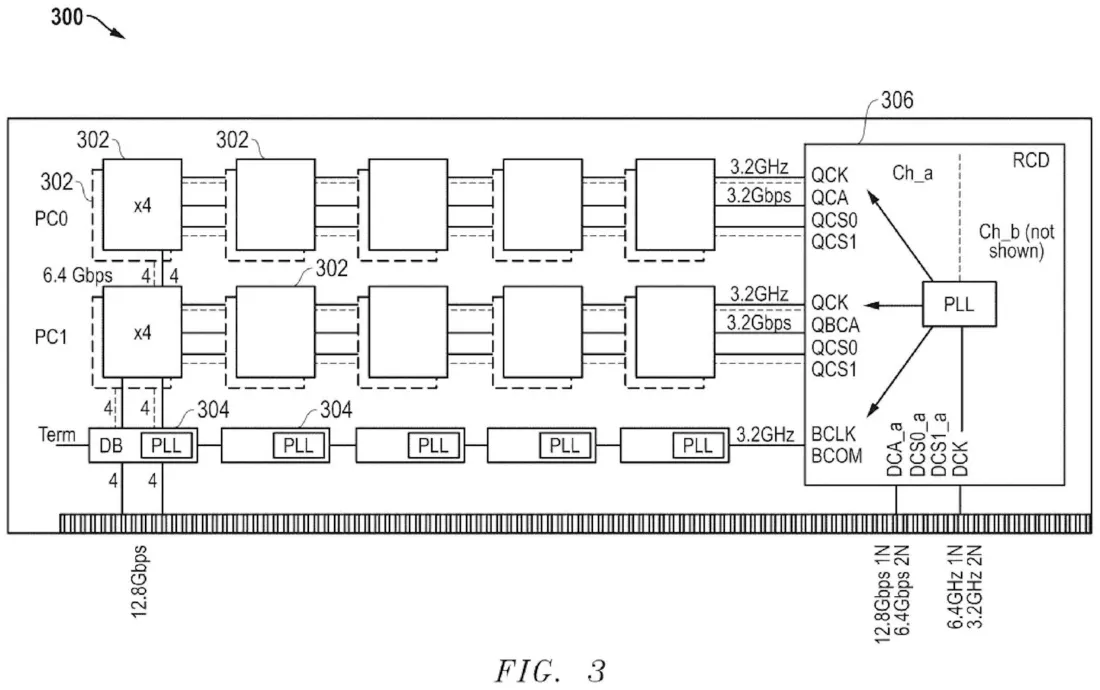

该方案通过引入高带宽双列直插内存模组(HB-DIMM)结构,使内存总线的数据传输速率从目前常见的6.4 Gbps提升至12.8 Gbps,实现翻倍增长。同时,该设计还优化了信号完整性,并有助于降低访问延迟。

与重新设计DRAM芯片的路径不同,该项创新主要依赖于将多个DRAM器件与先进的数据缓冲芯片进行集成耦合。缓冲芯片在其中承担关键角色,能够有效调度和管理信号传输路径,从而提升整体输出性能。

架构核心包含一个集成寄存器时钟驱动电路,可对内存指令进行解码,并依据芯片标识位实现命令路由。这一机制支持将内存操作分配至多个可独立寻址的“伪通道”,实现真正意义上的并行数据访问,突破传统内存模组顺序访问带来的带宽限制,为系统整体性能提升提供支持。

该内存架构支持1n与2n两种操作模式,在时钟同步和信号控制方面具备更高灵活性,有利于优化时序表现并增强信号稳定性。此外,设计中采用了一种简化的非交错传输格式,取代传统的交错式配置,进一步减少了数据传输过程中的延迟。

值得一提的是,该模组可在伪通道模式与四通道(quad-rank)配置之间动态切换,使其能够适应不同应用场景的需求,尤其适用于高性能计算等对数据吞吐能力和运行灵活性要求较高的环境。